[本帖為轉載帖]

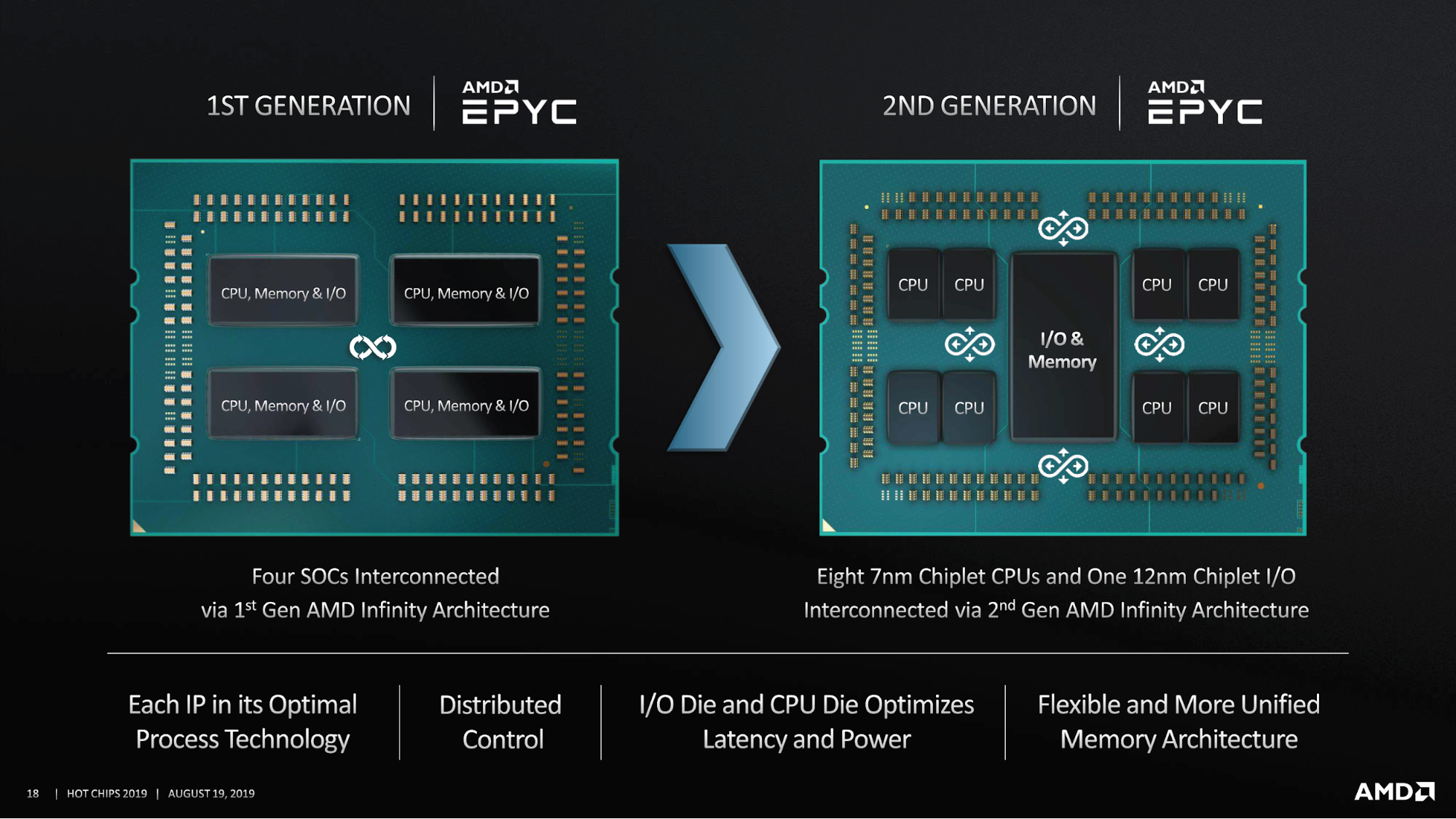

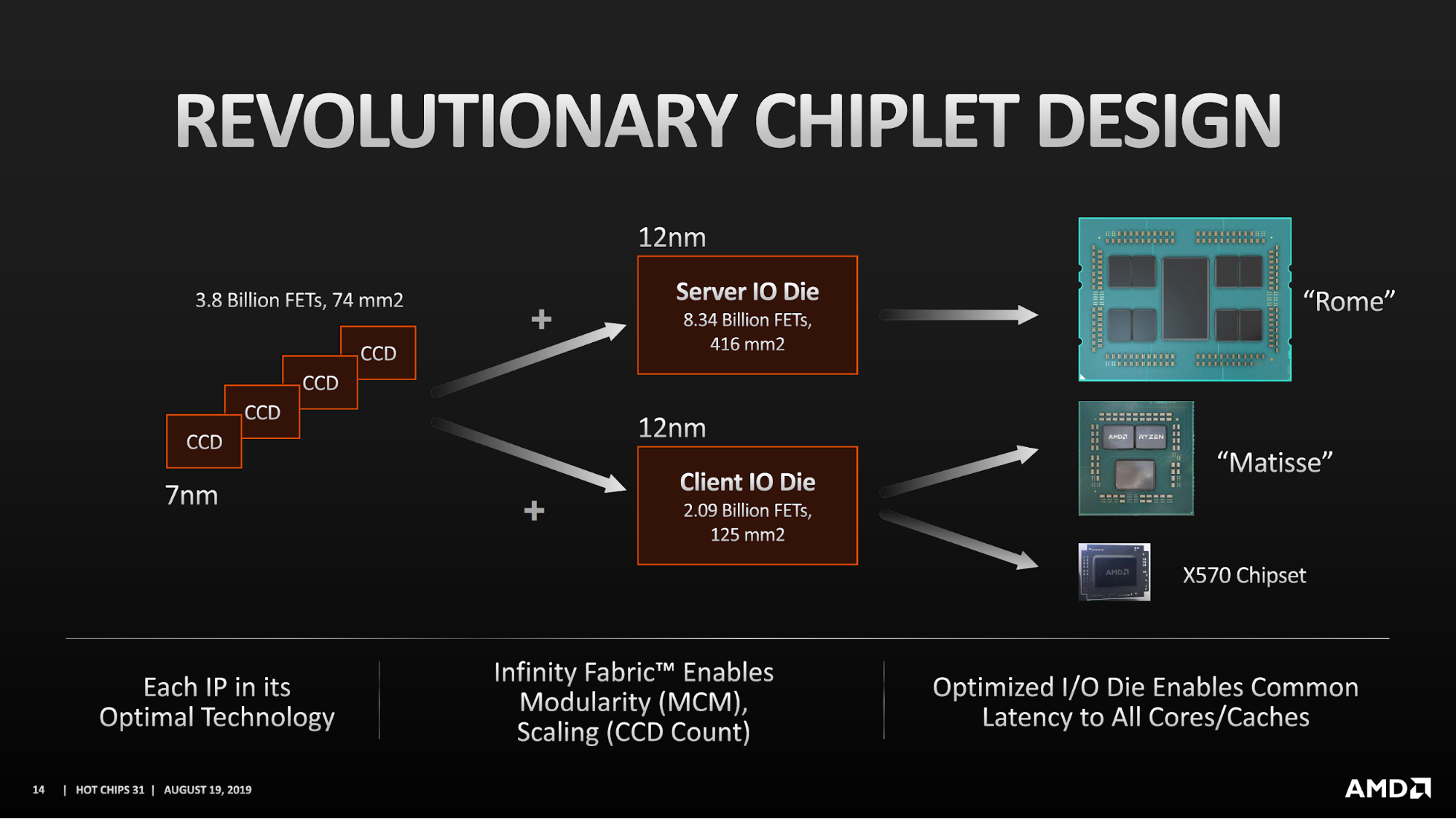

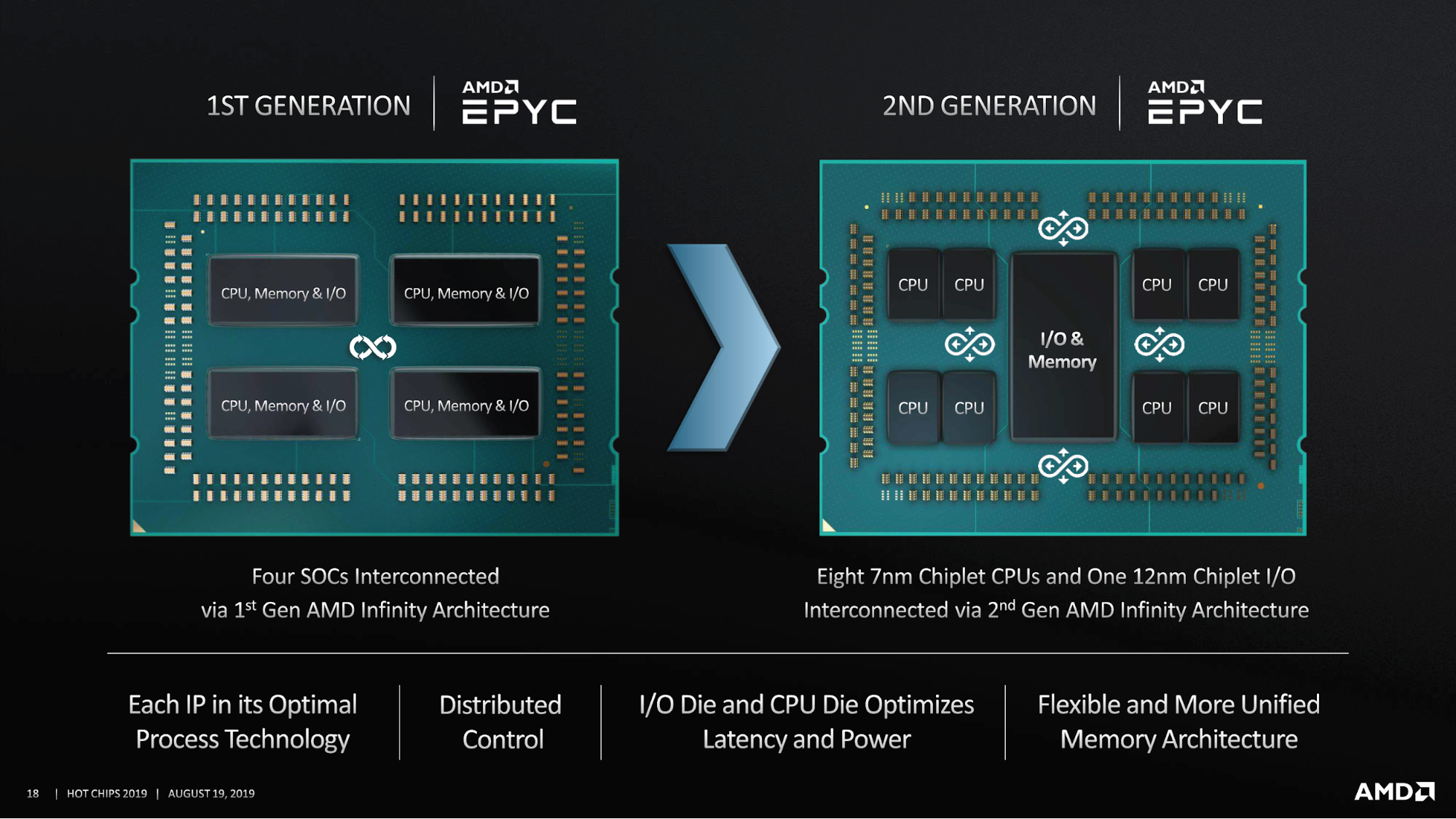

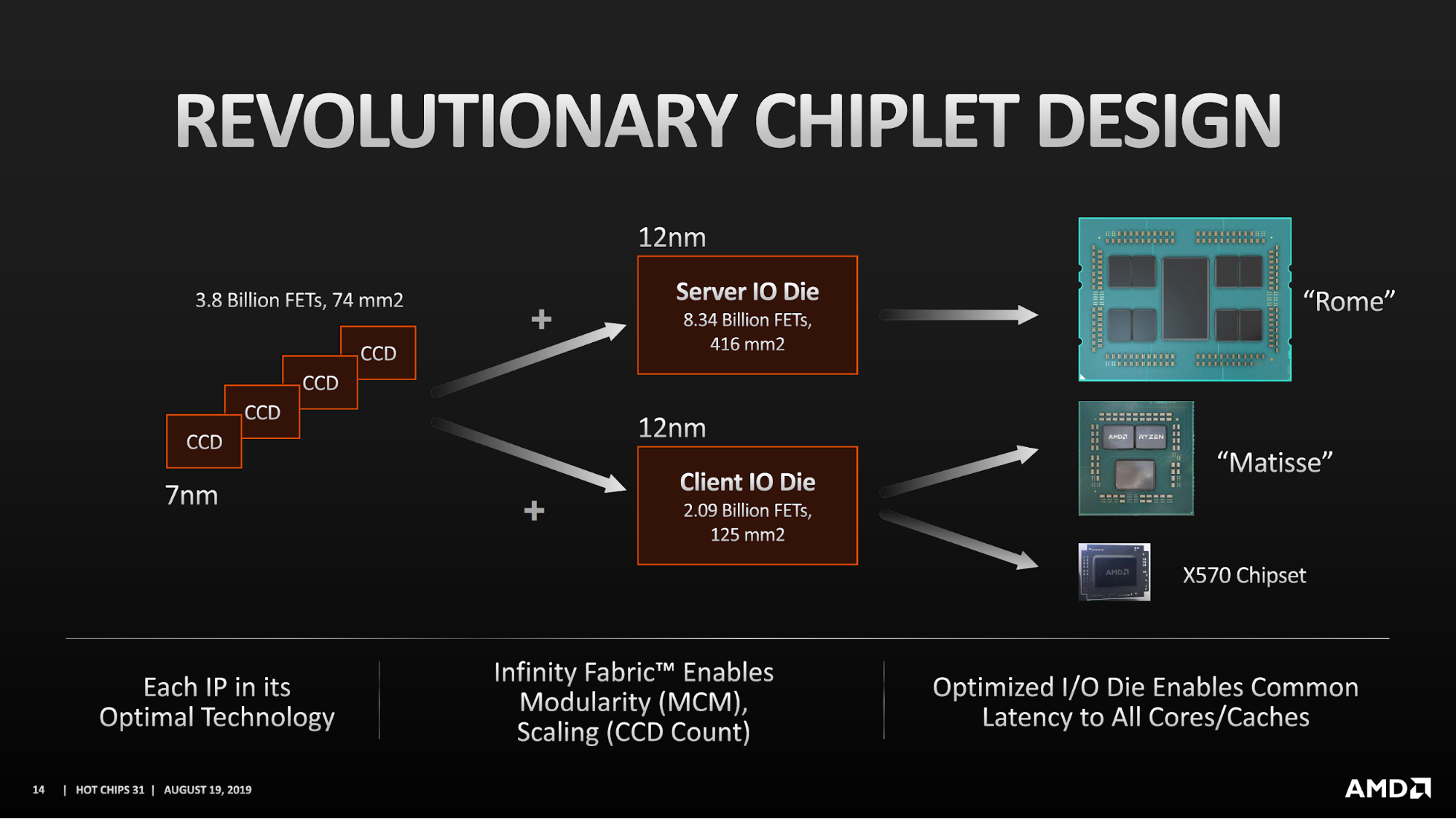

[size=1.14em]2019年12月9日「美國PTT」Reddit有[size=1.14em] ,大意是這樣的:台雞店... 呃,[size=1.14em]替[size=1.14em]代工生產的7nm製程8核心CCD (Core Complex Die),單一晶粒面積只有74平方公釐(這數字眾多紛紜,以AMD官方公佈為主),以完整8核心都可正常運作的標準,良率高達93.5%,一片12吋晶圓可取得749個8核心晶片,足以用來生產187顆32核心的EPYC或著93顆64核心EPYC。「反觀」28核心的Intel的14nm製程Xeon,Cascade Lake XCC單一晶粒高達928平方公釐(32 x 29mm,筆者對此存疑,太大了,接近700比較合理),在相同的晶圓缺陷率,只有46%晶粒無缺陷,意味著一片12吋晶圓只能產出24顆,完全看不到AMD的車尾燈。然後全世界的鄉民們都集體高潮了。 台積電的5nm投產測試順便同場加映,台積電幾乎剛好在同一時間的IEEE IEDM大會,公佈其5nm製程測試晶片良率高達80%—雖然試產樣品只是功能簡單的SRAM和小型SoC—但也足以讓客戶開始進行實際投產測試了,特別是像這種超級大客戶。 總之,AMD的「Chiplet多餡水餃」策略就此功德圓滿,只研製5顆晶片(加上CES發布的Renoir APU Ryzen 4000系列,以及最近ISSCC 2020透露的某入門級晶片),就打造了包含系統晶片組的完整產品線。  延伸閱讀:

硬科技:

硬科技:

硬科技:

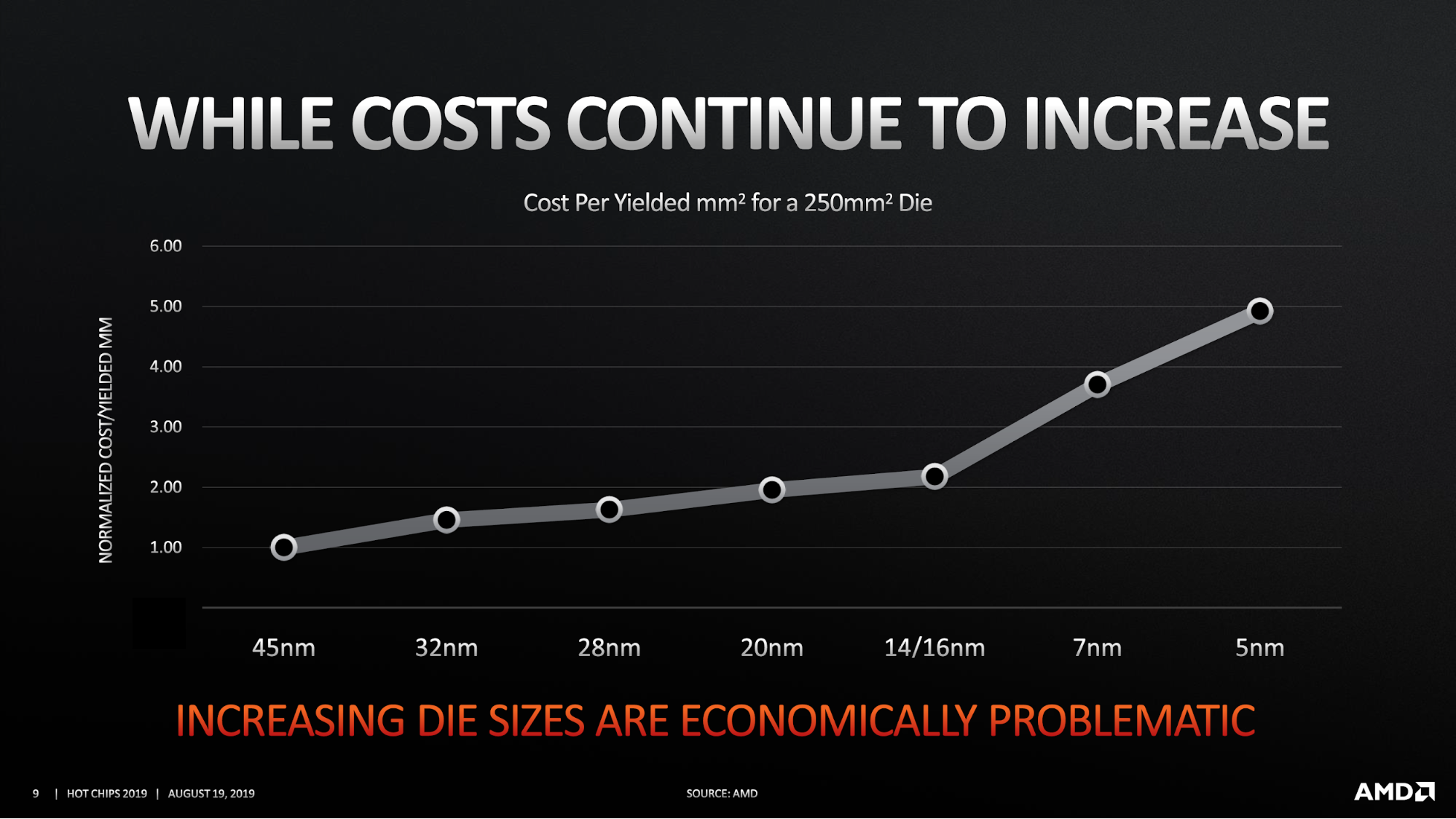

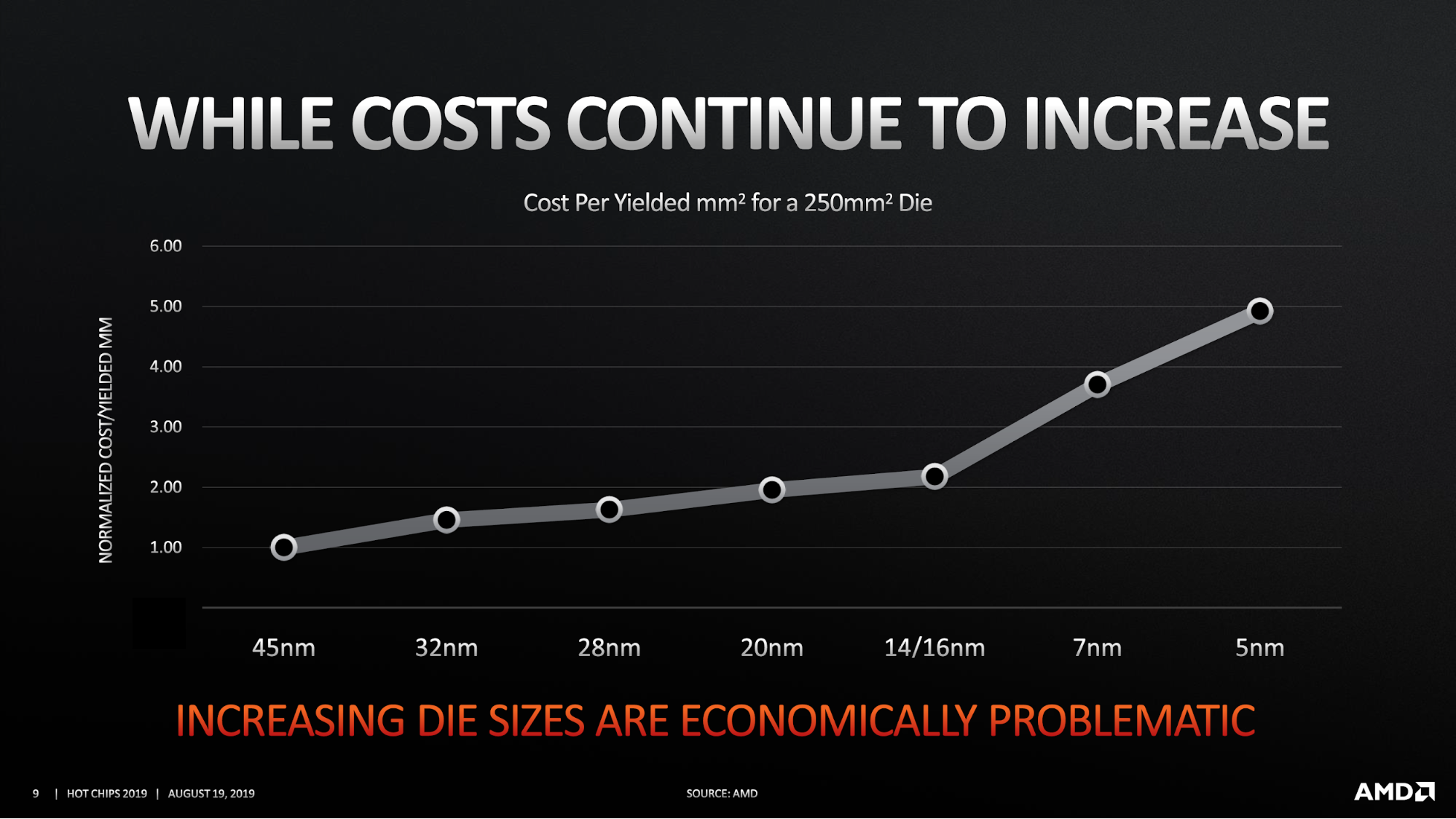

成本並不能單看表面但就此立馬論斷「AMD對Intel享有壓倒性的成本優勢」也未免太小看各位站在時代浪頭的科科了,有誰知道台積電一片7nm晶圓報給AMD多少錢?又有誰知道Intel自己內部那被擠牙膏連擠好幾年的14nm製造成本是多少?拜託,這些都是敏感到極點的商業機密耶。 更何況,AMD的Chiplet策略,如其說「高瞻遠矚」,還不如說「不得不然」,因為先進製程的成本是越來越高,從7nm開始,除了鉅額的研發成本,導入EUV(極紫外線)更讓微影光刻設備成本高達前代的2倍(短期內大概只剩下台積電、三星和Intel有能力負擔),所謂羊毛出在羊身上,這些費用當然最終都由客戶買單。即使從AMD已公開的資料推算,7nm的電晶體密度可到達14nm的1.7倍,但單位電晶體的成本很可能是不減反增的,如果先不考慮AMD簡報中的數據來自「250平方公釐」的話。 為何AMD會刻意挑出「250平方公釐」這個指標?原因很簡單:AMD在32nm/28nm製程的中高階APU,晶粒面積大約介於228到250,而14nm製程APU則是210,反觀剛發表的7nm APU「Renoir」卻只有149,大幅降低成本的意圖,顯而易見。  不過,AMD的Chiplet策略卻成為一面鏡子,照出了Intel全球CPU大缺貨的最可能主因:高階產品的晶粒太大,吃掉太多產能(偏偏所有產品幾乎都擠在14nm),而且是不得不使用更大的晶粒才能抗衡AMD的高階產品,這在2010年AMD開始從伺服器市場節節敗退到重新站穩腳跟的2018年之間數年,根本是完全讓人無法想像的情境。(未完待續)

... |

狗仔卡

狗仔卡

分享

分享 收藏

收藏 支持

支持 提升卡

提升卡